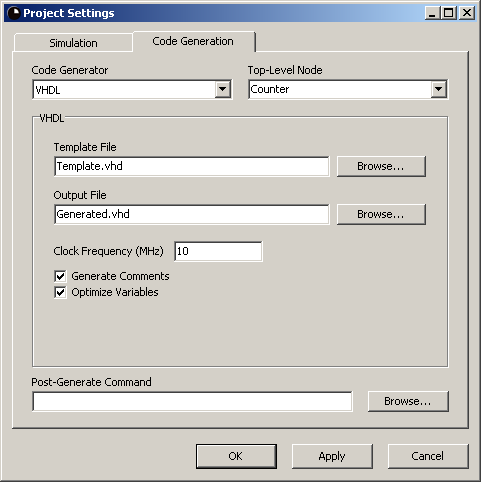

Template File. The template file for code generation. See the Code Generator - General section for an explanation of the template file. The path can be both absolute or relative to the project folder, that is, the folder containing the project file. Click the Browse... button to the right of the field to select the template file using a file dialog.

Output File. The location and name of the file to generate. The path can be both absolute or relative to the project folder, that is, the folder containing the project file. Click the Browse... button to the right of the field to select the location and name using a file dialog.

Clock Frequency (MHz). The frequency in MHz of the clock that will drive the implementation. This setting specifies what the %FREQUENCY_MHZ% key in the template file will be translated to in the code generation. It also determines the output value of the Dt block, which is used in the definitions of, among others, the Derivative and the Integral blocks. The value of Dt will be 1 / (clock frequency * 1,000,000). The clock frequency must be greater than 0.

Generate Comments. When checked, each generated assignment will be followed by a comment that indicates what signals are involved in the operation. As an example, i(1) <= i(2) + i(3); could be followed by -- sum <= pre_count + v1;. While this option makes the generated file bigger, it also makes it a little more human-readable.

Optimize Variables. When checked, the generated code will be optimized. As a consequence, some internal signals may be removed. This means that the caller of the generated code can not assume that all signals in the source files will also exist in the code. However, the input and output signals of the top-level node will always be available.